2025.06.20

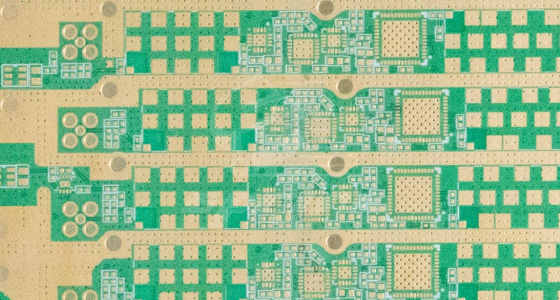

2025.06.20在存算一体芯片研发至量产的流程中,测试环节是确保芯片功能稳定、性能达标的核心环节。存算一体芯片测试板作为该环节的核心载体,承担芯片与测试设备的连接功能,直接影响测试数据准确性与测试过程稳定性,是验证存算一体芯片“存算协同”核心能力的关键组件。

存算一体芯片通过存储单元与计算单元深度融合,打破传统“数据存储-搬运-计算”的分离模式,其测试需求涵盖计算单元算力与精度验证、存储单元读写速度、容量及稳定性测试,以及“存算协同”状态下的数据传输效率与功耗控制考核。存算一体芯片测试板PCB的核心功能为上述测试需求提供支撑,具体包括以下三方面:

信号中转:实现存算一体芯片引脚与外部测试设备的精准连接,将芯片输出的计算结果、存储状态等信号无失真传输至测试设备,同时将测试设备发出的控制指令传输至芯片。针对存算一体芯片高频信号及“存算协同”时的并行数据传输需求,需保障信号传输完整性,避免信号反射、串扰导致的测试数据偏差。

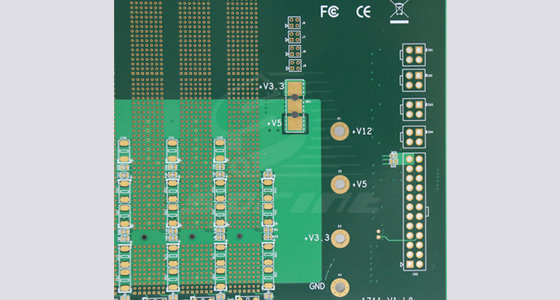

供电支持:针对存算一体芯片不同工作模式(纯存储模式、纯计算模式、存算协同模式)下的功耗差异,配置多组供电回路,匹配芯片不同模块的电压需求。通过电源平面布局优化与滤波配置,抑制供电噪声,确保芯片在测试过程中供电稳定,避免供电波动对测试结果真实性的影响。

多场景测试适配:结合存算一体芯片在边缘计算、AI推理、数据中心等应用场景的性能需求,预留测试接口与扩展点位,支持芯片算力、功耗、延迟、存储带宽等多维度参数测试。同时兼容不同规格散热模组,模拟芯片在不同散热条件下的工作状态,确保测试结果覆盖实际应用场景。

存算一体芯片测试数据精度直接决定芯片是否符合设计目标,测试板PCB需通过以下性能特性,满足高精度测试与高稳定运行需求:

信号完整性保障:存算一体芯片“存算协同”时的数据传输以高速并行信号为主,信号在PCB走线中若出现衰减或延迟,将导致测试设备接收信号与芯片实际输出信号偏差,影响芯片性能判断。因此,测试板PCB需采用高玻璃化转变温度、低介损基材,控制走线长度与阻抗匹配,减少信号反射与串扰,保障高速信号传输完整性。

电源完整性保障:存算一体芯片计算单元与存储单元工作时产生的瞬时电流波动,若遭遇电源平面高阻抗,将引发电压波动,影响芯片逻辑电平稳定性,甚至导致测试过程中芯片误操作。测试板PCB通过增大电源平面面积、优化电源平面与接地平面布局,降低电源阻抗,抑制电源噪声,保障芯片供电稳定。

机械稳定性保障:测试过程中,测试板PCB需与测试治具、芯片散热器进行多次组装与拆卸,且可能面临温度变化。为避免板体结构强度不足导致的焊点开裂、走线断裂,需采用加厚基板、增设加固边框或金属支撑结构,同时选用耐高温阻焊剂与焊盘材料,确保板体在频繁操作与温度变化环境下的机械稳定性。

存算一体芯片测试板PCB的制造工艺直接影响其测试可靠性,量产与使用过程中需重点控制以下工艺环节:

焊盘工艺:针对存算一体芯片高密度封装的小引脚间距特性,需严格控制焊盘尺寸偏差,采用无铅喷锡或沉金等表面处理工艺。沉金工艺可提升焊盘抗氧化性与连接可靠性,避免焊盘氧化导致的芯片与板体接触不良,保障信号传输与供电稳定性。

过孔工艺:为实现多层布线,需通过过孔实现不同层间的信号与电源连接。针对高速信号走线,过孔寄生电感与电容会影响信号完整性,需采用盲孔、埋孔替代传统通孔,减少过孔对信号的干扰,同时降低板体厚度。需严格控制过孔孔径与孔壁厚度,避免过孔导通不良导致的测试中断。

检测工艺:出厂前需开展外观检测与电气性能测试。外观检测需排查板体表面划伤、阻焊剂脱落、焊盘变形等缺陷;电气性能测试通过专业设备验证板体导通性、绝缘性与阻抗匹配性。针对存算一体芯片测试需求,还需开展高温高湿环境测试与振动测试,验证板体在长期使用场景下的可靠性,确保测试周期内性能稳定。

存算一体芯片测试板PCB是验证芯片性能、保障芯片质量的关键组件,通过信号中转、供电支持与多场景测试适配,为存算一体芯片测试提供基础支撑;依托信号完整性、电源完整性与机械稳定性保障,确保测试精度与运行稳定性;通过焊盘、过孔与检测工艺控制,保障测试可靠性。在存算一体技术发展进程中,该组件对芯片从研发到市场化的推进具有重要支撑作用。

2025.06.20

2025.06.20

2025.06.20

2025.06.20

2025.06.20

2025.06.20

采购咨询,获取商机

小红书

小红书

公众号

公众号

抖音

抖音

视频号

视频号

TOP

TOP