2025.06.20

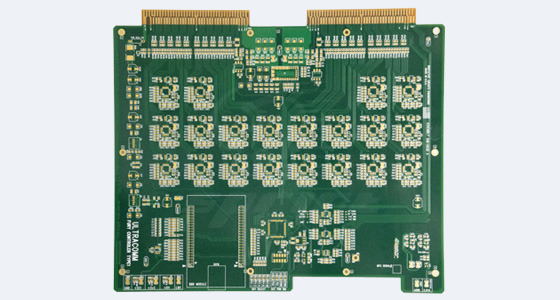

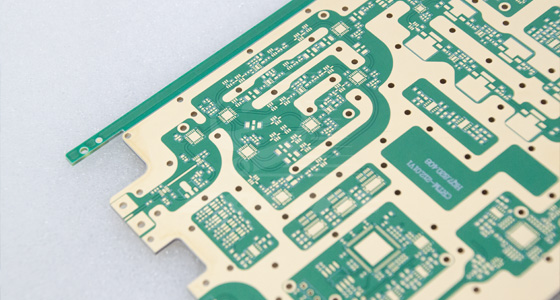

2025.06.20半导体设备中,12层PCB承担着连接核心芯片、传输高频信号与大电流的关键作用,其制造过程需满足极高的精度、稳定性与可靠性要求。相较于普通多层PCB,12层PCB的结构更复杂、工艺环节更多,且需适配半导体设备对信号完整性、散热性的严苛标准,因此制造过程中存在多个核心难点。下面从关键工艺环节出发,拆解12层PCB在半导体设备应用场景下的制造挑战。

层压是12层PCB制造的核心环节,需将12层基材、铜箔与绝缘层通过高温高压整合为一个整体,其难点集中在层间对齐精度与厚度均匀性两方面,这对半导体设备的信号传输至关重要。

从层间对齐来看,12层PCB需经过多次压合,每次压合时都需保证各层图形的对位误差控制在极小范围。但实际制造中,基材在高温下易发生热变形,且每次压合后的板材平整度会出现细微偏差,叠加到12层后,总对位误差可能突破临界值。一旦对齐精度不达标,半导体设备中高频信号的传输损耗会明显增加,甚至出现信号串扰,影响设备正常运行。

厚度均匀性同样棘手。12层PCB需控制整体厚度及每层厚度的偏差范围。但压合过程中,压力分布不均、基材与绝缘层的收缩率差异,会导致最终板材出现“中间厚、边缘薄”或局部凸起的问题。对于半导体设备中需要安装精密连接器的区域,厚度偏差超标会导致连接器接触不良,增加设备故障风险。

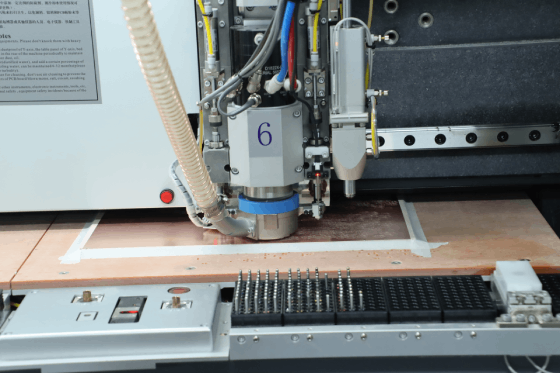

半导体设备12层PCB需大量微孔实现层间电路连接,这些微孔不仅尺寸小,还需穿透12层基材,深径比远超普通多层PCB,制造难度大幅提升。

首先是钻孔精度问题。由于孔径极小,钻嘴在高速旋转时易出现“颤振”,导致孔径偏差,甚至出现孔壁划伤。同时,12层基材的材质差异会导致钻嘴磨损速度加快,若未及时更换,后续微孔的孔径精度会持续下降。对于半导体设备而言,微孔孔径偏差会导致电镀后孔内铜层厚度不均,电流传输时局部发热加剧,影响设备散热性能。

更深层次的挑战在于孔壁质量。12层PCB的微孔需经过“钻孔-去钻污-电镀”流程,其中去钻污环节需清除孔壁残留的树脂碎屑,但微孔的窄孔径导致清洗液难以充分渗透,若去钻污不彻底,电镀时铜层无法与孔壁紧密结合,后期使用中易出现“孔壁剥离”,造成电路断路。此外,深径比过大使得电镀时电流难以均匀分布到孔底,孔底铜层厚度不足,在半导体设备的大电流场景下,孔底铜层易因过热烧毁。

半导体设备12层PCB对铜厚的要求具有“双重性”:一方面,全局铜厚需均匀,保证信号传输稳定;另一方面,部分区域需局部加厚铜厚,增强散热与载流能力,这两种需求在制造中易产生矛盾。

全局铜厚均匀性的难点在于电镀环节。12层PCB面积通常较大,电镀槽内电流分布易受板材形状、挂具位置影响,导致板材边缘与中心铜厚存在差异。此外,12层PCB的微孔和盲孔会“分流”电流,使得孔附近区域的表面铜厚比其他区域薄。若全局铜厚偏差过大,半导体设备中不同路径的信号传输速度会出现差异,导致数据同步延迟,影响设备处理效率。

局部加厚铜厚则面临“过度电镀”风险。为实现局部加厚铜厚,需在对应区域进行二次电镀,但二次电镀时,电流易向周边区域扩散,导致非目标区域铜厚超出标准。同时,局部加厚区域与周边常规铜厚区域的过渡处易出现“台阶”,后续阻焊层涂覆时,台阶处易产生气泡或厚度不足,导致铜层暴露,增加半导体设备的氧化与短路风险。

半导体设备12层PCB的阻焊层需同时满足“薄涂层”与“高绝缘性”要求,以适配设备内部紧凑的安装空间与高压工作环境,但这两个需求在制造中存在天然矛盾。

薄涂层的涂覆精度难以控制。阻焊层通常采用丝印或喷涂工艺,对于12层PCB表面的细微凹凸,薄涂层易出现“漏涂”或“厚度不均”。例如,丝印时刮刀压力控制不当,在台阶处的阻焊层厚度可能低于标准值。而阻焊层过薄会导致绝缘性能下降,半导体设备中高压信号传输时易出现击穿现象,引发设备故障。

高绝缘性则对阻焊剂材质与固化工艺提出严苛要求。半导体设备工作时,PCB长期处于高温环境,且可能接触腐蚀性气体,阻焊剂需具备优异的耐高温与耐腐蚀性。但薄涂层下,阻焊剂中的固化剂分布易出现不均,导致固化后部分区域交联密度不足,在高温环境下易出现开裂,绝缘性能随使用时间推移快速下降。

半导体设备12层PCB需具备极高的平整度,否则会影响与芯片、散热器的贴合度,导致散热不良或装配失效。但12层PCB的多层结构与复杂工艺,使其平整度控制成为制造中的“顽疾”。

一方面,多层压合后的应力释放会导致板材翘曲。12层PCB在多次压合过程中,各层材料的内应力会不断累积,冷却后应力释放,易使板材向铜箔较厚的一侧弯曲。尤其是当局部铜厚差异较大时,翘曲度可能远超半导体设备要求。

另一方面,后续工艺的高温处理会加剧平整度问题。阻焊固化等工艺需在一定高温下进行,在此温度下,PCB板材会再次发生热变形,若此前应力未充分释放,变形量会进一步叠加。对于半导体设备中需要与散热片紧密贴合的区域,平整度偏差会导致接触面积减少,散热效率下降,芯片工作温度升高,缩短设备使用寿命。

半导体设备12层PCB的制造过程需100%全检,但由于结构复杂,部分缺陷难以检测,且返修难度极高,成为质量把控的一大难点。

在检测环节,12层PCB的内层缺陷难以通过常规外观检测发现,需依赖X光检测与超声波扫描。但X光检测对微小缺陷的识别率有限,且无法判断孔壁与内层铜箔的结合状态;超声波扫描虽能检测层间结合情况,但受限于12层的厚度,扫描分辨率会下降,可能遗漏局部脱粘区域。这些未检测出的缺陷,在半导体设备长期运行中会逐渐扩大,最终引发电路故障。

返修环节的挑战更大。若检测出内层短路或微孔电镀不良,需对12层PCB进行“分层返修”,即逐层剥离绝缘层与铜箔,修复缺陷后重新压合。但分层过程中,高温与化学试剂易损伤周边完好层,导致返修成功率较低。即使返修成功,重新压合后的区域也可能出现新的应力集中,在半导体设备的振动环境下,返修处易出现裂纹,成为新的故障隐患。

半导体设备12层PCB的制造难点,本质是“高精度需求”与“复杂结构工艺”的矛盾:既要满足多层结构的精准整合,又要适配微孔、局部铜厚等特殊设计;既要保证全局工艺稳定性,又要应对局部区域的特殊要求。这些难点不仅需要先进的设备支撑,更依赖工艺参数的精细化调控与全流程质量监控。只有攻克这些难点,才能制造出符合半导体设备要求的12层PCB,为设备的稳定、高效运行奠定基础。

2025.06.20

2025.06.20

2025.06.20

2025.06.20

2025.06.20

2025.06.20

采购咨询,获取商机

小红书

小红书

公众号

公众号

抖音

抖音

视频号

视频号

TOP

TOP