2025.07.23

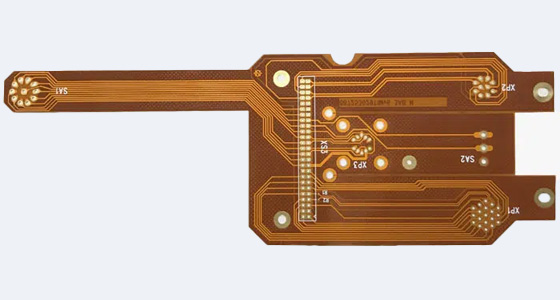

2025.07.23PCB作为电子系统的关键载体,其性能直接关乎整个系统的稳定性与可靠性。而PCB阻抗控制,正是保障高速高频电子电路信号完整性的核心技术,它如同电子信号的“护航员”,确保信号在传输过程中稳定、准确地抵达目的地。

阻抗是电路对电流阻碍作用的综合体现,在PCB传输线这个微观世界里,它由分布的电阻、电容和电感共同构成。当信号在传输线上飞驰时,若传输线的阻抗与信号源、负载的阻抗不匹配,就如同道路突然变窄或出现障碍,信号会发生反射,原本规整的信号波形出现过冲、下冲和振铃等畸变现象,同时信号强度也会在传输过程中不断衰减,导致接收端难以准确识别信号,最终影响整个电路系统的正常运行。例如,在高速数据传输的USB3.0接口电路中,若PCB阻抗控制不当,数据传输就会出现错误,甚至无法正常传输数据。

传输线的几何参数如同塑造阻抗的“模具”,对其有着直接且显著的影响。线宽是其中敏感的参数之一,一般来说,线宽越宽,传输线的横截面积增大,电阻减小,同时线间电容增大、电感减小,使得特性阻抗降低;反之,线宽越窄,特性阻抗越高。以常见的50Ω阻抗传输线为例,在某特定叠层结构和材料的PCB中,可能需要将线宽精确控制在0.15mm左右才能满足阻抗要求。

线长的变化同样不可忽视,随着线长增加,信号在传输过程中所经历的电阻、电容和电感的累积效应增强,不仅导致信号衰减加剧,还会使特性阻抗发生变化。在高频电路中,过长的传输线就像漫长而崎岖的道路,信号在其中传输时损耗严重,容易引发信号完整性问题。

线间距作为传输线几何参数的重要组成部分,影响着线间电容和互感。合适的线间距能够减小线间串扰,保证信号的纯净度,同时也会对特性阻抗产生影响。较大的线间距会使线间电容和互感减小,特性阻抗增大;较小的线间距则会降低特性阻抗,但可能增加串扰风险。

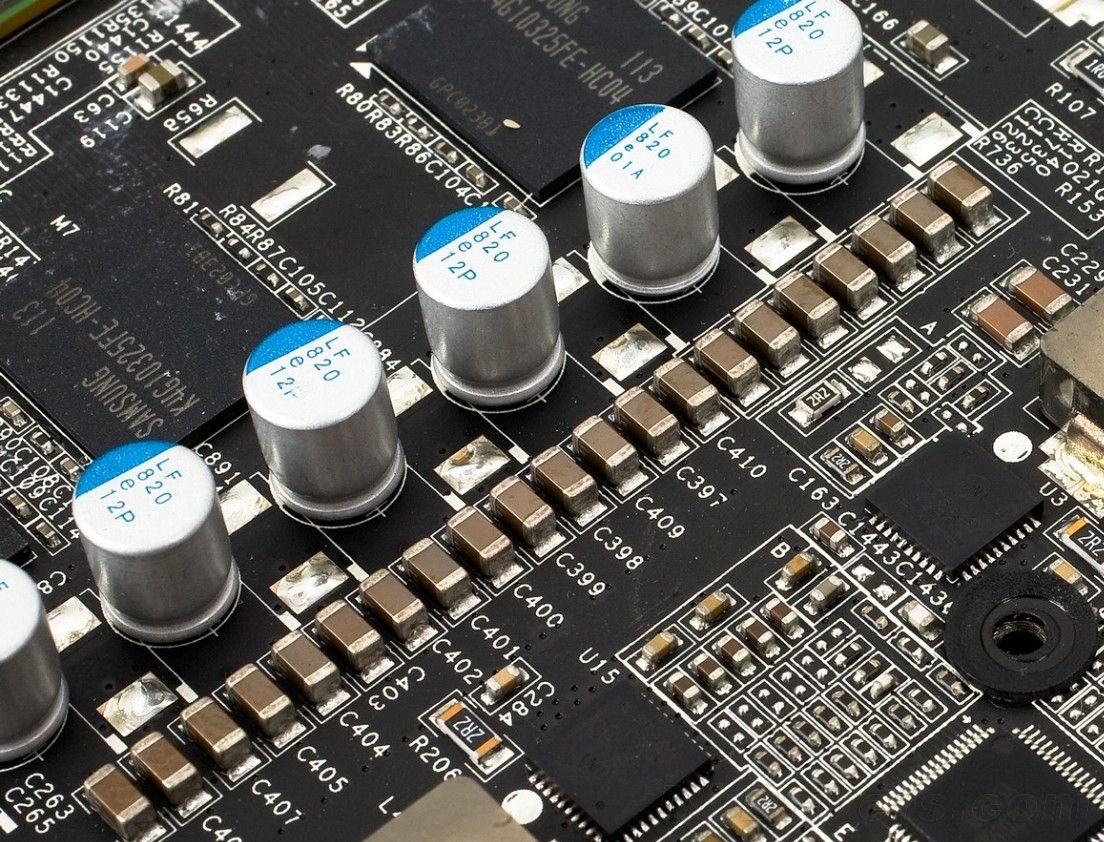

PCB材料特性是阻抗的内在决定因素。介电常数与阻抗呈反比关系,介电常数越大,传输线的电容越大,特性阻抗越低。不同类型的PCB板材介电常数差异明显,如普通的FR-4板材介电常数一般在4.2-4.6之间,适用于低频、对成本敏感的电路;而高频板材聚四氟乙烯(PTFE)介电常数较低,通常在2.2-2.6之间,常用于高频通信等对信号传输质量要求极高的领域。

介质损耗角反映了PCB板材在交变电场作用下的能量损耗程度,在高频电路中,介质损耗角过大就像一个“能量黑洞”,会大量消耗信号能量,导致信号衰减加剧。因此,在高频电路设计中,选择介质损耗小的板材是保证信号质量的关键。

参考平面在PCB阻抗控制中扮演着不可或缺的角色。传输线与参考平面之间的距离对阻抗有着直接影响,距离越近,电容越大,特性阻抗越低;反之则特性阻抗越高。在设计PCB叠层时,需要根据阻抗要求精确控制传输线与参考平面的距离,以实现目标阻抗。

参考平面的完整性也至关重要,若参考平面存在不连续或分割的情况,就如同道路出现断裂,会导致传输线的电流分布发生变化,进而改变阻抗。例如,在高速信号传输的PCB中,如果接地平面存在缝隙,会使传输线的回流路径受到影响,导致阻抗波动,严重影响信号完整性。

设计阶段是实现PCB阻抗控制的起点和蓝图规划阶段。合理的叠层布局是基础,需要综合考虑信号层、电源层和接地层的布局,以及各层之间的介质厚度和材料选择。通常会采用对称的叠层结构,确保信号层与参考平面之间的距离均匀,为信号传输提供稳定的环境。例如,在设计四层板时,可将电源层和接地层分别置于中间两层,上下两层作为信号层,通过合理设置各层之间的介质厚度,来实现对阻抗的初步控制。

精确的线宽和线间距计算是规划阶段的核心任务之一。借助专业的阻抗计算工具,如PolarSI9000、HyperLynx等,根据PCB材料特性、叠层结构以及期望的阻抗值,能够准确计算出传输线的线宽和线间距。在计算过程中,还需充分考虑制造公差的影响,适当预留余量,确保实际制造出的PCB满足阻抗要求。

对于高速电路中广泛应用的差分信号,其设计需要更加严格的把控。要严格控制差分对的线宽、线间距以及长度匹配,一般差分阻抗设计为100Ω。通过采用蛇形走线等方式调整差分对的长度,使两根传输线长度尽量相等,减少信号传输延迟差,保证差分信号的完整性。

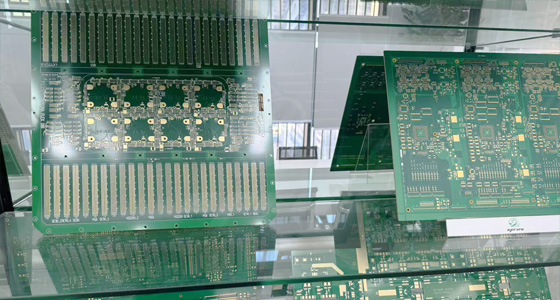

制造阶段是将设计蓝图转化为实际产品的关键环节,对PCB阻抗控制起着决定性作用。在材料选择方面,要挑选介电常数精确且稳定、介质损耗小的板材,确保从源头上为阻抗控制提供保障。同时,要严格把控板材的质量,避免因材料批次差异导致的性能波动。

精密的加工工艺是制造阶段的核心。蚀刻工艺直接决定传输线的线宽精度和边缘质量,需要精确控制蚀刻时间、蚀刻液浓度和温度等参数,防止蚀刻过度或不足导致线宽偏差。层压工艺影响介质厚度的均匀性,在层压过程中,要严格控制压力、温度和时间等参数,避免出现气泡和杂质,保证各层之间紧密贴合,介质厚度一致。电镀工艺关系到传输线的导电性和耐腐蚀性,精确控制电镀时间、电流密度等参数,确保电镀层厚度均匀,提升传输线的电气性能。此外,由于制造过程中不可避免地存在公差,如线宽公差、介质厚度公差等,需要在设计阶段就进行制造公差补偿,通过适当调整设计参数,减小制造公差对阻抗的影响。

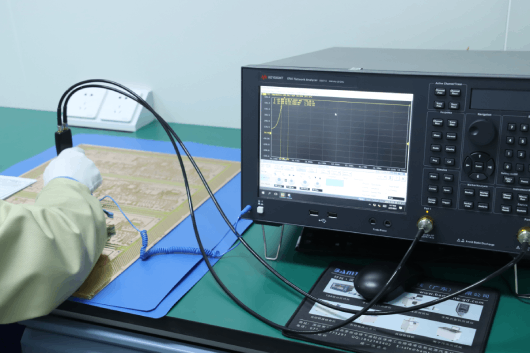

完成PCB制造后,测试与验证是确保阻抗达标的最后一道关卡。时域反射计(TDR)是常用的阻抗测试仪器,它通过向传输线发送高速脉冲信号,并测量反射回来的信号,能够快速、准确地计算出传输线的阻抗值以及阻抗不连续点的位置。网络分析仪则主要用于测量射频和微波电路的S参数,通过对S参数的分析计算,获取传输线在不同频率下的阻抗特性,为高频电路的阻抗测试提供详细信息。

在得到测试结果后,需要进行深入分析。若测试结果与设计值偏差在允许范围内,说明PCB的阻抗控制符合要求;若超出允许偏差范围,则需要仔细排查原因,可能涉及设计计算错误、制造工艺偏差、材料性能波动等。针对不同原因,采取相应的优化措施,如调整设计参数、改进制造工艺或更换材料,并再次进行阻抗测试,直至测试结果满足设计要求。

PCB阻抗控制贯穿于PCB设计、制造和测试的全过程,每一个环节都至关重要。只有深入理解影响阻抗的因素,并在各个阶段采取科学合理的措施,才能实现精确的阻抗控制,为高速高频电子电路的稳定运行提供坚实保障,推动电子技术不断迈向新的高度。

2025.07.23

2025.07.23

2025.06.20

2025.06.20

2025.06.20

2025.06.20

采购咨询,获取商机

小红书

小红书

公众号

公众号

抖音

抖音

视频号

视频号

TOP

TOP