2025.06.20

2025.06.20高频高速电路领域,PCB阻抗特性直接决定了信号传输的完整性与稳定性。阻抗不匹配会引发信号反射、衰减、串扰等问题,严重时甚至导致整个电路系统失效。因此,PCB阻抗控制技术成为保障高频高速电路性能的核心环节。下面将从阻抗控制的基础认知出发,深入解析其关键技术要点,重点围绕材料选择、结构参数控制、制程工艺优化及检测验证展开,为行业从业者提供专业参考。

阻抗控制的核心目标是使PCB传输线的特性阻抗与两端连接的器件阻抗保持一致,以更大限度减少信号在传输过程中的能量损耗与干扰。特性阻抗并非单一电阻值,而是由传输线的分布电阻、分布电容、分布电感共同决定的复数阻抗,其大小与PCB的物理结构、材料特性及制程工艺密切相关。

在高频高速场景下(如5G通信、服务器、航空航天电子等),信号波长缩短,传输线的分布参数对信号的影响急剧放大,阻抗控制精度要求极高,部分严苛场景下精度要求更为严格,这对后续技术环节提出了极高要求。

基材与覆铜箔是决定PCB阻抗特性的基础物质载体,其性能参数直接影响阻抗控制精度。

基材的介电常数:介电常数是基材关键的参数之一,特性阻抗与介电常数的平方根成反比,介电常数的微小波动会直接导致阻抗偏移。不同类型基材的介电常数差异明显,高频高速场景常用低介电常数基材,更适合低损耗信号传输。实际应用中,需根据电路工作频率选择介电常数稳定、温度系数低的基材,避免因环境温度变化导致介电常数波动,进而影响阻抗稳定性。

覆铜箔的厚度与粗糙度:覆铜箔的厚度直接影响传输线的分布电阻,厚度越小,分布电阻越大,对阻抗的影响越显著。高频高速PCB通常采用薄铜箔,以减少趋肤效应带来的信号损耗。同时,铜箔表面粗糙度也会影响信号传输,粗糙度越大,信号在传输过程中的散射损耗越严重,尤其在高频场景下,表面粗糙度对阻抗的影响不可忽视。因此,需选择表面粗糙度低的电解铜箔或压延铜箔,确保阻抗稳定性。

传输线的物理结构参数是决定特性阻抗的核心,主要包括线宽、线距、介质厚度(传输线与参考平面之间的距离),不同结构的传输线(如微带线、带状线、差分线)需针对不同参数进行精准控制。

微带线:微带线是PCB表面常见的传输线结构,由信号线、基材(介质层)和下方的参考平面(地或电源层)组成,其特性阻抗主要与线宽、介质厚度及基材介电常数相关。制程中,线宽和介质厚度的控制精度要求极高,否则极易导致阻抗偏移,超出精度要求。

带状线:带状线位于PCB内部,被上下两个参考平面包裹,信号线周围均为介质层,其特性阻抗除与线宽、基材介电常数相关外,还与上下参考平面的距离及信号线到上下参考平面的距离相关。由于带状线被介质层完全包裹,信号受外部干扰更小,但制程中介质厚度的控制难度更高,需确保介质层压合后的厚度均匀性,避免因厚度不均引发阻抗偏移。

差分线:差分线由两根平行的信号线组成,通过差分信号传输减少共模干扰,其阻抗控制包括特性阻抗(单端阻抗)和差分阻抗(两根信号线之间的阻抗)。差分阻抗通常与单端阻抗存在固定比例关系,主要与线宽、线距及介质厚度相关。线距的控制精度要求严格,若线距偏差过大,会导致差分阻抗偏离设定值,影响差分信号的完整性。

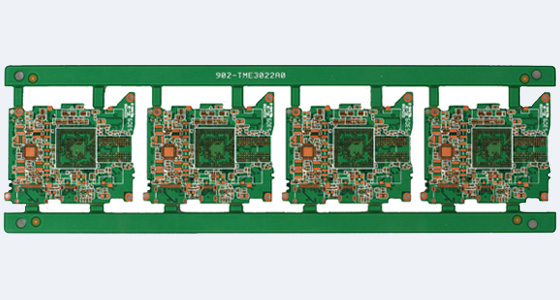

PCB制程工艺是将参数转化为实际产品的关键环节,从基材裁切、层压、图形转移到蚀刻、阻焊涂覆,每一步工艺都可能影响阻抗精度,需通过精细化管控确保阻抗稳定。

层压工艺是将多层基材与铜箔压合为一体的过程,直接决定介质厚度的均匀性与稳定性,是阻抗控制的核心工艺之一。

压力与温度的协同管控:层压时需根据基材特性设定合理的压力与温度曲线(升温速率、保温温度、保温时间)。若压力不足,基材与铜箔之间可能存在空隙,导致介质厚度不均匀;若温度过高或保温时间过长,基材可能发生过度固化,导致介电常数变化,进而影响阻抗。需通过实时监控确保温度和压力偏差控制在合理范围内。

层压对齐度控制:多层PCB层压时,各层传输线与参考平面的对齐度直接影响介质厚度的一致性。若对齐偏差过大,会导致部分区域的介质厚度变薄或变厚,引发阻抗局部偏移。因此,需采用高精度定位设备,确保层压对齐度偏差控制在合理范围内,同时在层压后通过专业检测设备检查层间对齐情况,及时剔除不合格产品。

图形转移是将设置的传输线图形转移到铜箔上的过程,蚀刻则是去除多余铜箔,形成最终传输线,这两个工艺直接决定线宽的精度,进而影响阻抗。

图形转移的精度控制:图形转移通常采用光刻工艺,包括涂胶、曝光、显影三个步骤。涂胶时需确保光刻胶厚度均匀,避免因胶厚不均导致曝光后图形边缘模糊;曝光时需控制曝光能量与曝光精度,采用高精度曝光机,确保图形线宽与设定值的偏差控制在合理范围内;显影时需控制显影时间与显影温度,避免显影不足或显影过度。

蚀刻工艺的参数优化:蚀刻工艺需根据铜箔厚度设定蚀刻液浓度、蚀刻温度与蚀刻速度。蚀刻速度过快易导致线宽过度减小,速度过慢则可能导致蚀刻不彻底,残留铜箔影响阻抗。同时,需采用喷淋式蚀刻设备,确保蚀刻液均匀喷淋在铜箔表面,避免局部蚀刻不均导致线宽偏差。蚀刻后需通过光学检测设备检查线宽精度,对超出偏差的产品及时返工或报废。

阻焊层(绿油)涂覆与表面处理(如沉金、镀锡)虽不直接决定阻抗,但处理不当仍可能影响阻抗稳定性。

阻焊层的厚度控制:阻焊层覆盖在传输线表面,其介电常数与厚度会对微带线的阻抗产生轻微影响(带状线因被介质层包裹,受阻焊层影响较小)。若阻焊层厚度不均匀,会导致微带线周围的介电环境不一致,进而引发阻抗局部波动。因此,阻焊涂覆时需控制涂层厚度,偏差控制在合理范围内,同时避免阻焊层覆盖传输线的关键区域。

表面处理的一致性:表面处理的目的是防止铜箔氧化,确保焊接可靠性,但处理层的厚度与均匀性也会影响传输线的电阻。若处理层厚度不均匀,会导致传输线表面电阻波动,进而影响阻抗。因此,需控制表面处理的工艺参数,确保处理层厚度偏差控制在合理范围内,同时通过外观检测与厚度测试确保一致性。

阻抗检测与验证是PCB阻抗控制的最后一道防线,通过专业设备与方法检测实际产品的阻抗值,确保其符合要求,同时为制程工艺优化提供数据支撑。

目前主流的PCB阻抗检测设备为阻抗测试仪,检测方法主要包括时域反射法(TDR)与频域法。

时域反射法:TDR通过向传输线发送一个快速上升沿的脉冲信号,根据信号反射情况计算特性阻抗。该方法可直观显示传输线各点的阻抗变化(如阻抗突变位置、突变幅度),适合检测阻抗的局部异常(如线宽偏差、介质厚度不均)。检测时需将测试探头与PCB上的测试点精准连接,确保接触良好,测试频率需覆盖高频高速电路的工作范围。

频域法:频域法通过测量传输线在不同频率下的散射参数,计算特性阻抗。该方法可分析阻抗随频率的变化规律,适合评估PCB在整个工作频率范围内的阻抗稳定性。

阻抗检测并非终点,而是通过数据分析发现制程中的问题,进而优化工艺参数。例如,若检测发现某批次PCB的微带线阻抗普遍偏低,需排查是否存在线宽偏大、介质厚度偏小或基材介电常数偏高等问题,定位问题根源后调整相应工艺参数。同时,需建立阻抗检测数据库,记录每批次PCB的检测数据,通过统计分析总结工艺参数与阻抗的相关性,形成标准化的工艺管控方案,持续提升阻抗控制精度。

PCB阻抗控制是一项系统性技术,需从材料选择、结构参数控制、制程工艺优化到检测验证全环节协同发力。在高频高速电路需求日益增长的背景下,阻抗控制精度的要求将不断提高,这不仅需要从业者掌握核心技术要点,更需通过精细化管理与持续创新,应对复杂的制程挑战。未来,随着新型基材、高精度制程设备与智能化检测技术的发展,PCB阻抗控制技术将朝着更高精度、更高稳定性、更高效益的方向迈进,为电子信息产业的高质量发展提供坚实支撑。

2025.06.20

2025.06.20

2025.08.29

2025.08.29 2025.12.08

2025.12.08

采购咨询,获取商机

小红书

小红书

公众号

公众号

抖音

抖音

视频号

视频号

TOP

TOP