2025.06.20

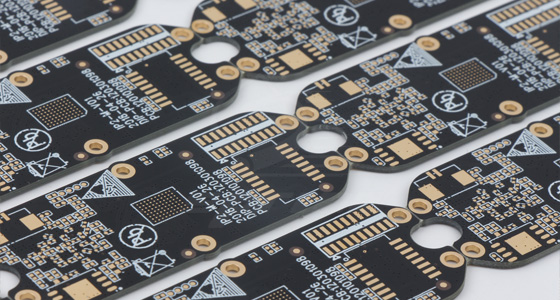

2025.06.20电子设备不断向小型化、高性能化发展的趋势下,厚铜PCB因其出色的电流承载能力和良好的散热性能,在电源模块、汽车电子、高功率LED驱动器等众多领域得到了广泛应用。然而,厚铜PCB在制造过程中面临着诸多挑战,其中蚀刻工艺的复杂性尤为突出。随着铜层厚度的增加,蚀刻过程中的侧蚀、过蚀以及蚀刻不均匀等问题愈发严重,这不仅会导致线路宽度和形状的偏差,还可能影响PCB的电气性能和可靠性。因此,开发有效的蚀刻补偿方案对于保证厚铜PCB的制造质量至关重要。

铜厚超200μm时,蚀刻液横向侵蚀导致线路宽度损失可达设计值的30%以上。例如400μm厚铜蚀刻后,线宽偏差常超过±100μm,严重破坏微线宽电路的信号完整性。

厚铜完全蚀刻需延长工艺时间或提高药液浓度,易引发线路过度腐蚀。实测数据显示,蚀刻时间每增加5%,线路断裂风险提升8-12%,直接导致良率下降。

宽线区域因蚀刻液交换效率低,蚀刻速率比窄线慢15-20%,造成同一块PCB上不同区域线路厚度偏差超过20μm,影响阻抗一致性。

通过预补偿算法抵消蚀刻损耗,核心公式为:补偿值=目标线宽-(蚀刻后实测线宽+侧蚀深度)通过工艺参数与蚀刻损耗的量化关联,在生产前预设补偿量,使蚀刻后线宽逼近设计值。例如200μm厚铜线路,预设补偿25μm可将蚀刻后线宽误差控制在±5μm

收集与蚀刻过程相关的各类参数,包括蚀刻液浓度、温度、时间、流速等。这些参数的变化会直接影响蚀刻速率和蚀刻效果,是后续建立蚀刻模型的重要依据。例如,蚀刻液浓度的升高通常会加快蚀刻速率,但也可能增加侧蚀的程度。

对不同宽度、不同形状的线路进行蚀刻实验,测量蚀刻后线路实际减少的尺寸,即蚀刻宽度损失。同时,通过显微镜等设备观察线路截面,记录侧蚀深度及形状变化。这些数据能够直观反映蚀刻工艺对线路的影响,为建立准确的蚀刻补偿模型提供基础数据。

在蚀刻宽度损失与设计宽度呈简单正相关的情况下,可以采用线性模型。假设蚀刻宽度损失ΔW与设计宽度W满足线性关系:ΔW=k×W+b,其中k和b为通过实验数据拟合得到的系数。线性模型计算简单,但仅适用于蚀刻工艺较为稳定、影响因素相对单一的情况。

考虑到实际蚀刻过程中,侧蚀等现象可能随线路宽度变化呈现复杂的非线性关系,如侧蚀深度可能随宽度增加呈指数增长。此时需要建立非线性模型,如多项式模型、指数模型等。以多项式模型为例,可表示为ΔW=a₀+a₁W+a₂W²+...+aₙWⁿ,通过最小二乘法等方法拟合实验数据确定各项系数a₀、a₁、...、aₙ。非线性模型能够更准确地描述蚀刻过程,但计算相对复杂。

利用大数据训练回归模型,如随机森林、支持向量机等。首先将收集到的大量蚀刻工艺参数数据、线路设计参数数据以及对应的蚀刻结果数据整理成训练集。然后使用这些数据对机器学习模型进行训练,模型通过学习数据中的规律,能够预测不同设计参数下的蚀刻补偿值。机器学习模型具有较强的适应性,能够处理复杂的非线性关系和多因素影响,但需要大量的数据支持和较高的计算资源。

根据建立的蚀刻补偿模型,计算每条线路所需的补偿值。常用公式为:补偿值=理想宽度-实际宽度+侧蚀深度。在实际计算中,还需考虑线路的具体情况,如在高密度布线区域,要考虑相邻线路间距的变化,避免因补偿过度导致线路短路。例如,当两条相邻线路的设计间距为D,在对其中一条线路进行补偿值计算时,如果补偿值过大,可能会使补偿后的线路与相邻线路间距小于安全间距,从而引发短路风险。此时,需要对补偿值进行适当调整,以确保相邻线路间距满足设计要求。

厚铜PCB蚀刻补偿方案对于解决厚铜PCB制造过程中的蚀刻难题、提高产品质量具有重要意义。通过合理的数据采集与分析、建立准确的蚀刻补偿模型、精确计算补偿值能够有效补偿蚀刻过程中的线路宽度损失,提高线路宽度的精度和一致性。同时,基于实时工艺监控的动态补偿和多工艺条件下通用补偿算法的开发,为蚀刻补偿方案的进一步优化提供了方向。

2025.06.20

2025.06.20

2025.06.20

2025.06.20

2025.06.20

2025.06.20

采购咨询,获取商机

小红书

小红书

公众号

公众号

抖音

抖音

视频号

视频号

TOP

TOP